Accelerator-Rich, Heterogeneous System Architectures

Project Overview

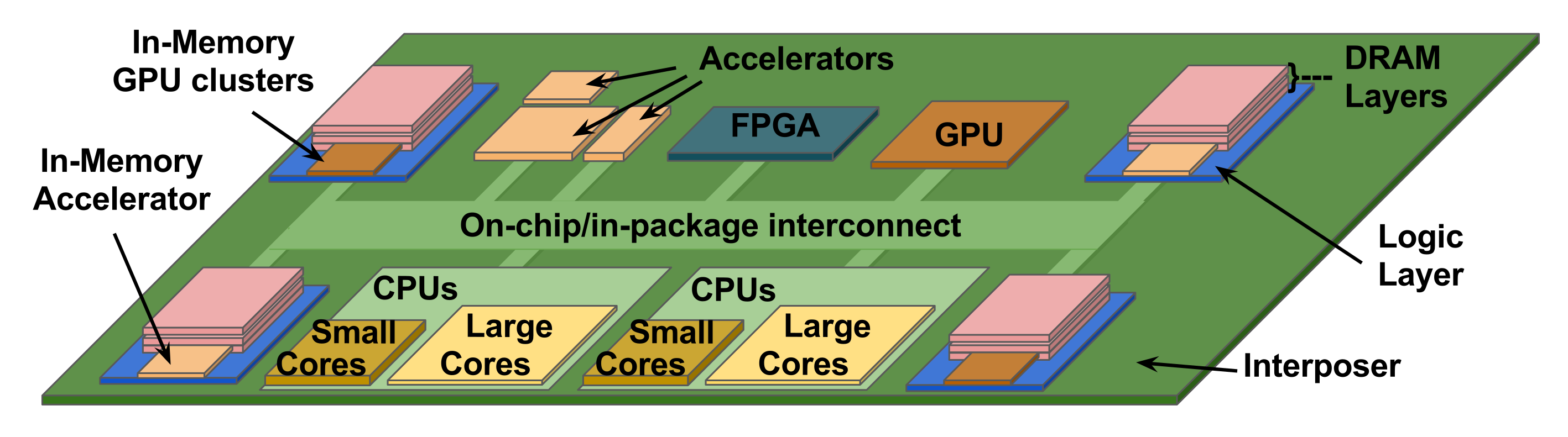

With architectural innovations and technology scaling reaching fundamental limits, energy efficiency is one of the primary design concerns today. It is well-accepted that specialization and heterogeneity can achieve both high performance and low power consumption, but there are fundamental tradeoffs between flexibility and specialization in determining the right mix of cores on a chip. Furthermore, with increasing acceleration, communication between heterogeneous components is rapidly becoming the major bottleneck, where architectural and runtime support for orchestration of data movement and optimized mapping of applications is critical. We study these questions through algorithm/architecture co-design of specialized architectures and accelerators for various domains, as well as novel architectures and tools for accelerator integration and heterogeneous system design.

Selected Publications

-

Dimitrios Gourounas, Austin James, Bagus Hanindhito, Arash Fathi, Lizy K. John, and Andreas Gerstlauer, "HighWave: Large-Scale High-Bandwidth Wave Simulations on FPGAs," Proceedings of the IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM), Fayetville, AR, May 2025.

[

pdf]

pdf]

-

Kishore Punniyamurthy and Andreas Gerstlauer, "TAFE: Thread Address Footprint Estimation for Capturing Data/Thread Locality in GPU Systems," Proceedings of the International Conference on Parallel Architectures and Compilation Techniques (PACT), virtual conference, October 2020.

[

pdf]

pdf]

-

Mochamad Asri, Dhairya Malhotra, Jiajun Wang, George Biros, Lizy K. John, and Andreas Gerstlauer, "Hardware Accelerator Integration Tradeoffs for High-Performance Computing: A Case Study of GEMM Acceleration in N-Body Methods," IEEE Transactions on Parallel and Distributed Systems (TPDS), vol. 32, no. 8, pp. 2035-2048, February 2021.

[

pdf]

pdf]

-

Mochamad Asri, Curtis Dunham, Roxana Rusitoru, Andreas Gerstlauer, and Jonathan Beard, "The Non-Uniform Compute Device (NUCD) Architecture for Lightweight Accelerator Offload," Proceedings of the Euromicro International Conference on Parallel, Distributed, and Network-Based Processing (PDP), Västerås, Sweden, March 2020.

[

pdf]

pdf]

-

Ardavan Pedram, Robert van de Geijn, Andreas Gerstlauer, "Codesign Tradeoffs for High-Performance, Low-Power Linear Algebra Architectures ," IEEE Transactions on Computers (TC), Special Issue on Energy Efficient Computing, vol. 61, no. 12, December 2012.

[

pdf]

pdf]

People

Daniel Peralta Velazquez

Master's/Ph.D. Student

Dimitrios Gourounas

Ph.D. Student

Kishore Punniyamurthy

2021, AMD Research, Austin, TX

Mochamad Asri

2020, Facebook (FRL), Menlo Park, CA

Ardavan Pedram

2013 (co-supervised with Prof. van de Geijn), post-doc at Stanford